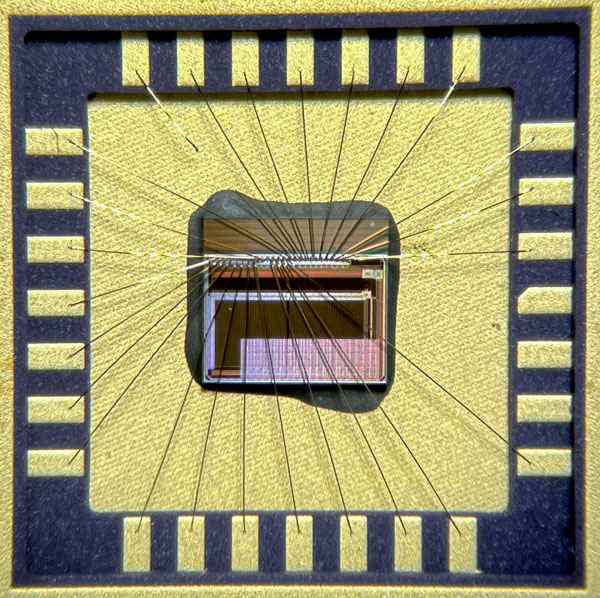

Разработанный чип содержит два массива памяти размером 64 × 64, объединённых в аналоговую петлю обратной связи с использованием встроенных операционных усилителей, цифро-аналоговых и аналого-цифровых преобразователей. Такая архитектура позволяет выполнять операции инверсии матриц непосредственно в памяти, без необходимости передачи данных во внешние вычислительные блоки. Экспериментально показано, что ускоритель способен эффективно решать системы дифференциальных уравнений методом рекурсивной блочной инверсии, демонстрируя экономию потребления до 5000 раз по сравнению с цифровыми аналогами этих цепей.

Источник изображения: Politecnico di Milano

Добавим, в основе массивов памяти лежат ячейки резистивной памяти ReRAM, которые схемотехнически связаны с ячейками SRAM. Ячейка ReRAM — это безусловно аналоговый элемент, задающий тон всей новой платформе. Также следует сказать, что в основе этой европейской разработки лежат проекты учёных из Пекинского университета, которые тоже публикуют научные работы на эту же тему. В целом — это пример международного сотрудничества, которое решает общую проблему повышения эффективности высокопроизводительных вычислений.

Практическая применимость предложенного решения продемонстрирована на задачах отслеживания траектории ракеты с использованием фильтра Калмана, а также на ускорении вычислений обратной кинематики в роботизированных манипуляторах. Полученные результаты по точности сопоставимы с полностью цифровыми системами при эквивалентной разрядности, при этом аналоговый подход с вычислениями в памяти обеспечивает выигрыш по задержке, энергопотреблению и занимаемой площади кристалла.